GTX_Maxwell:相当于要自己管理中间变量(寄存器)该如何被赋值,其实如果写cuda之类贴近底层的编程语言,也会遇到类似的问题

25-11-5 10:54 来自广东

田春冰河

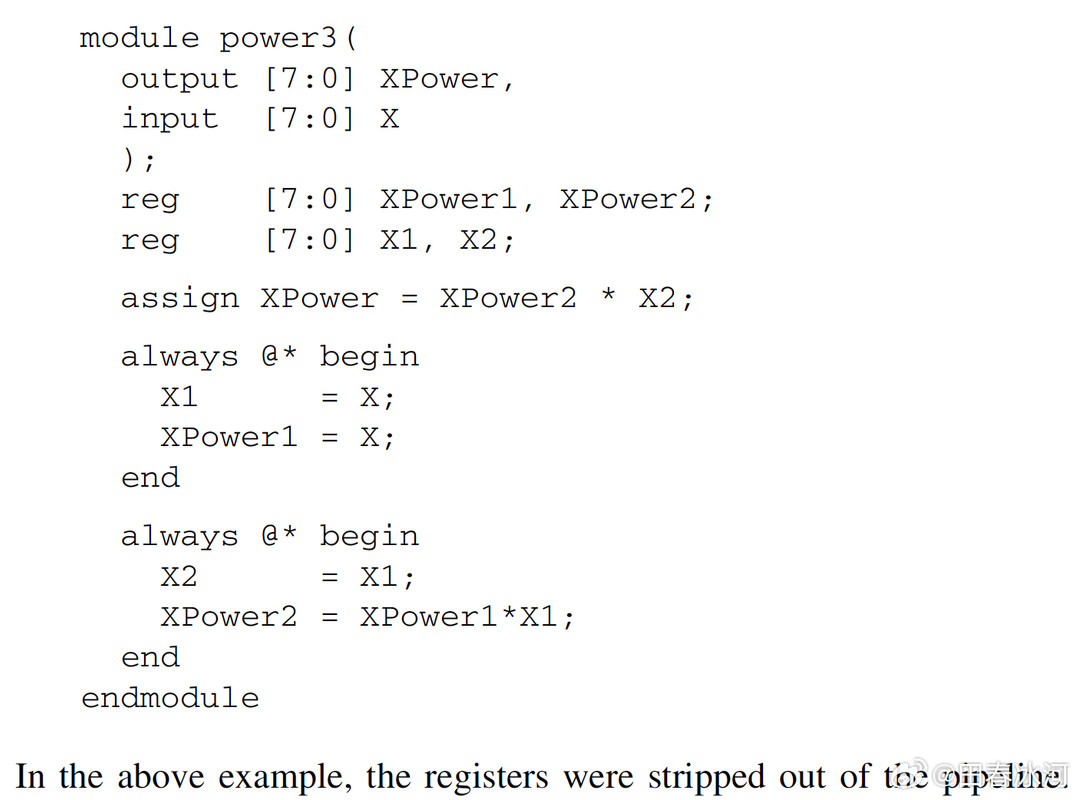

:差不多。不过如果只是想用一些局部变量把长表达式分拆成较小的,但却不改变综合后的电路形态,也是可以做到的。我最初的困惑之处只是因为那些中间寄存器看起来就像局部变量一样,但其实并不是。

25-11-5 11:57 来自澳大利亚

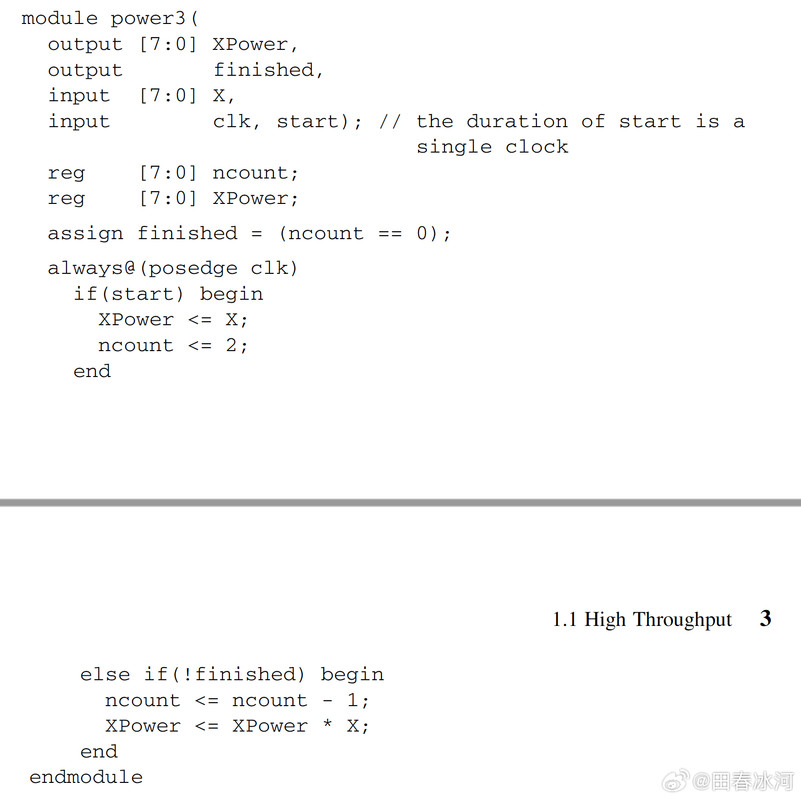

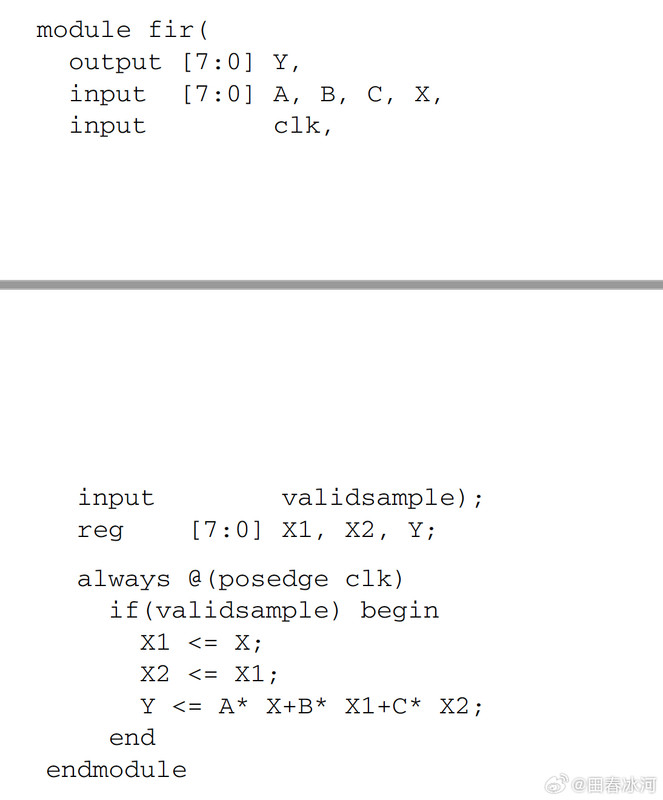

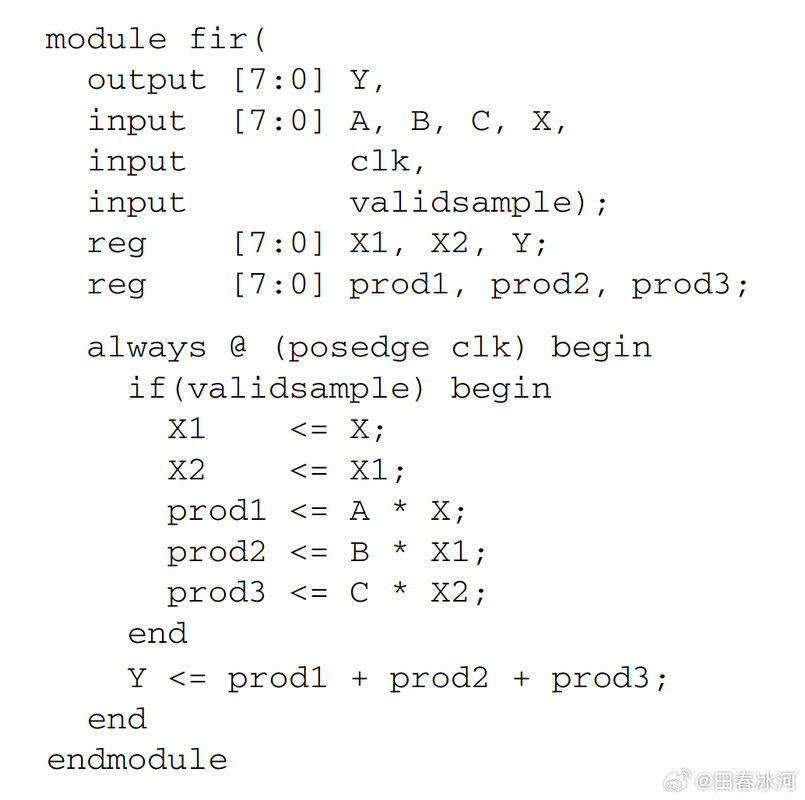

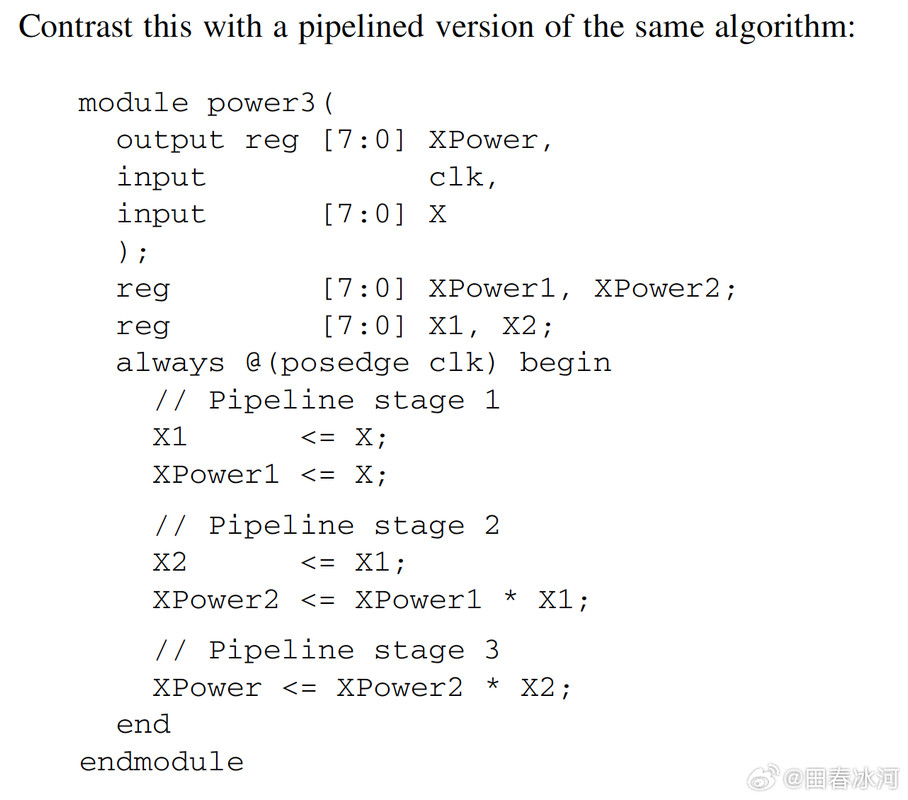

[1/3] 在数字电路里,把迭代循环展开成流水线可以大幅提高吞度量,但要牺牲芯片面积(FPGA 通常最缺的就是这个);去掉流水线中的寄存器可以大幅降低电路延迟,但要牺牲芯片的最大工作频率;要想提高工作频率可以增加中间寄存器将关键路径打断成较小的路径,但这又重新增加了延迟(不过幸好还有其他办法)。这些还都是小事,最缺德的是实现这些不同的设计思路对应的 VHDL/Verilog 代码从软件编程的视角看起来几乎没什么区别……

https://postimg.cc/gallery/fN34tD3

GTX_Maxwell:相当于要自己管理中间变量(寄存器)该如何被赋值,其实如果写cuda之类贴近底层的编程语言,也会遇到类似的问题

25-11-5 10:54 来自广东

田春冰河

:差不多。不过如果只是想用一些局部变量把长表达式分拆成较小的,但却不改变综合后的电路形态,也是可以做到的。我最初的困惑之处只是因为那些中间寄存器看起来就像局部变量一样,但其实并不是。

25-11-5 11:57 来自澳大利亚

No replies yet.