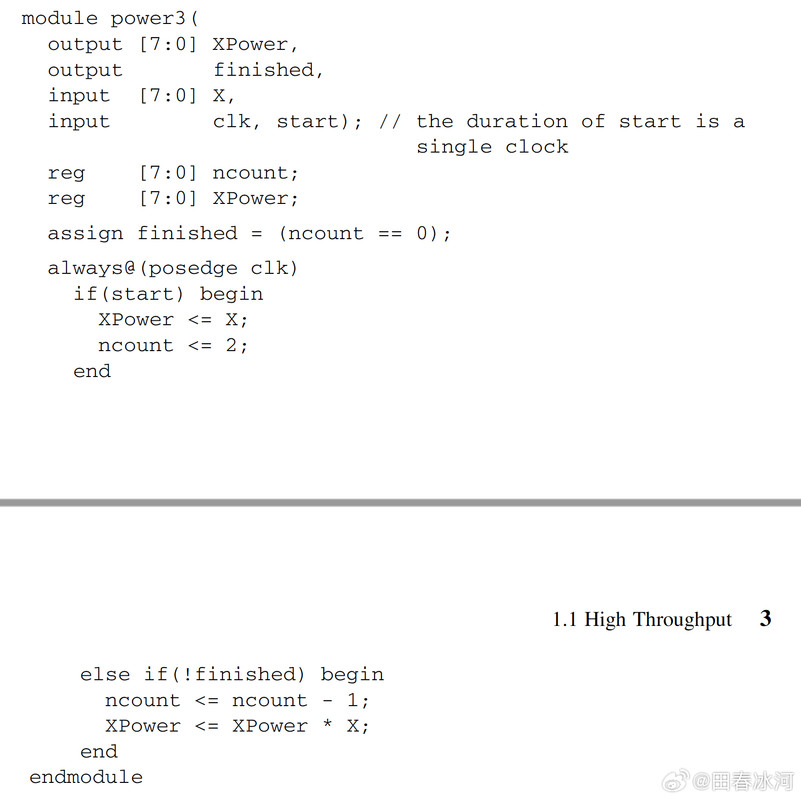

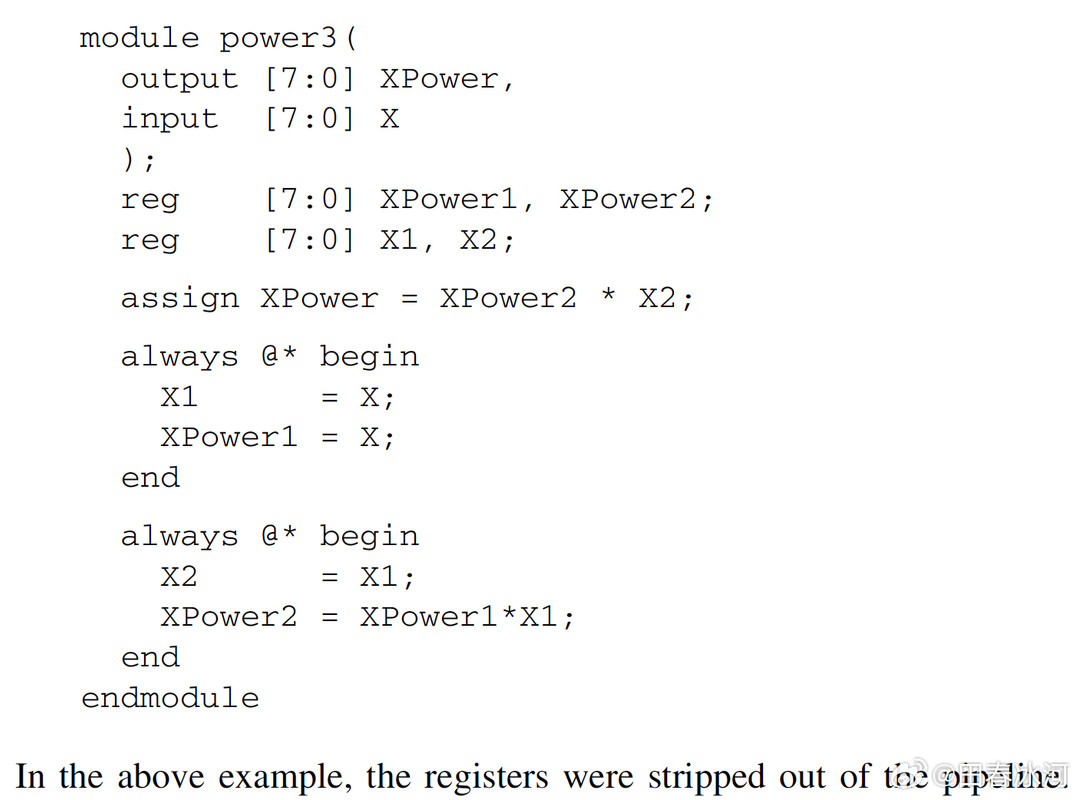

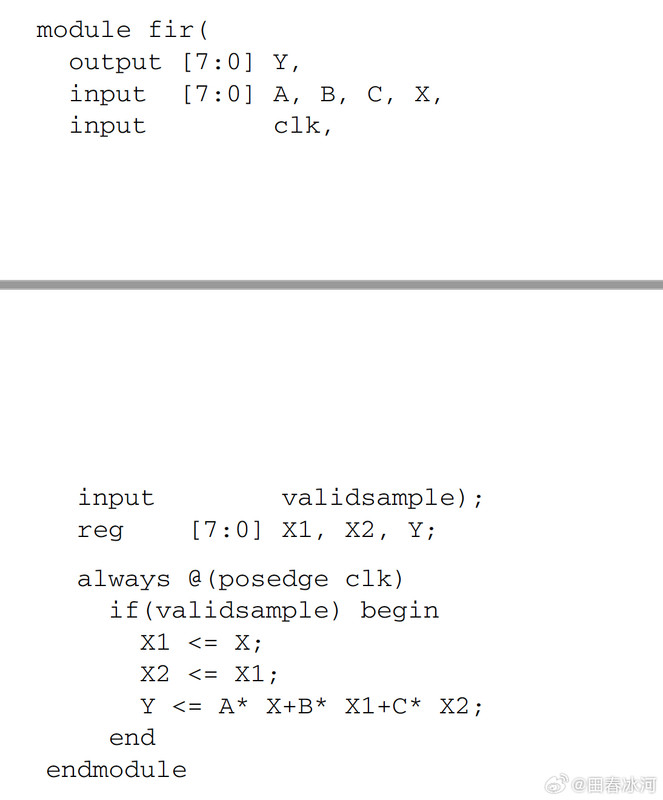

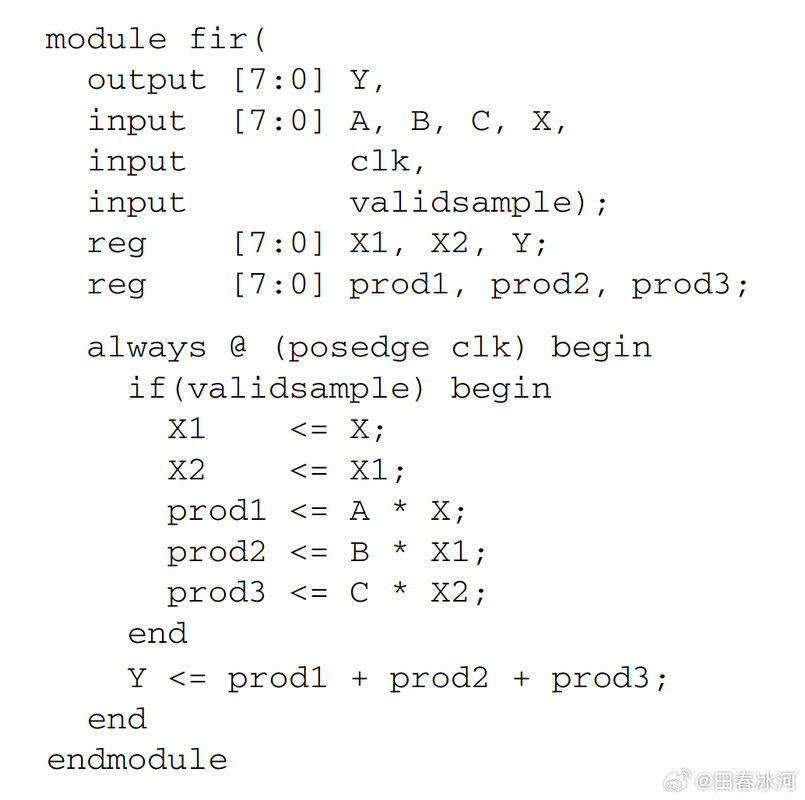

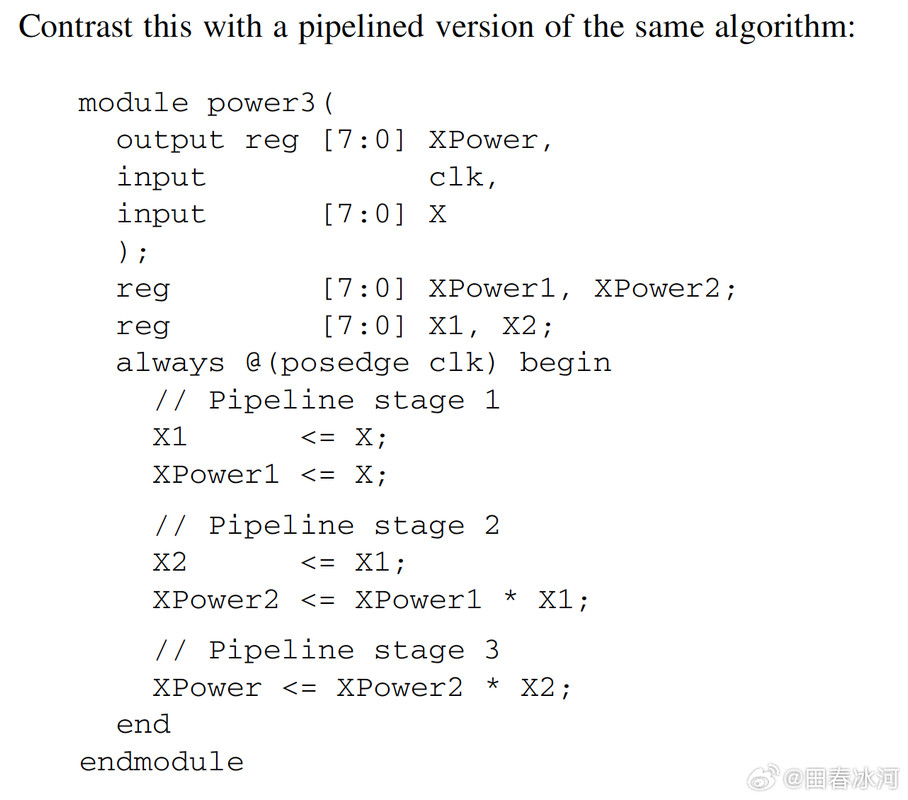

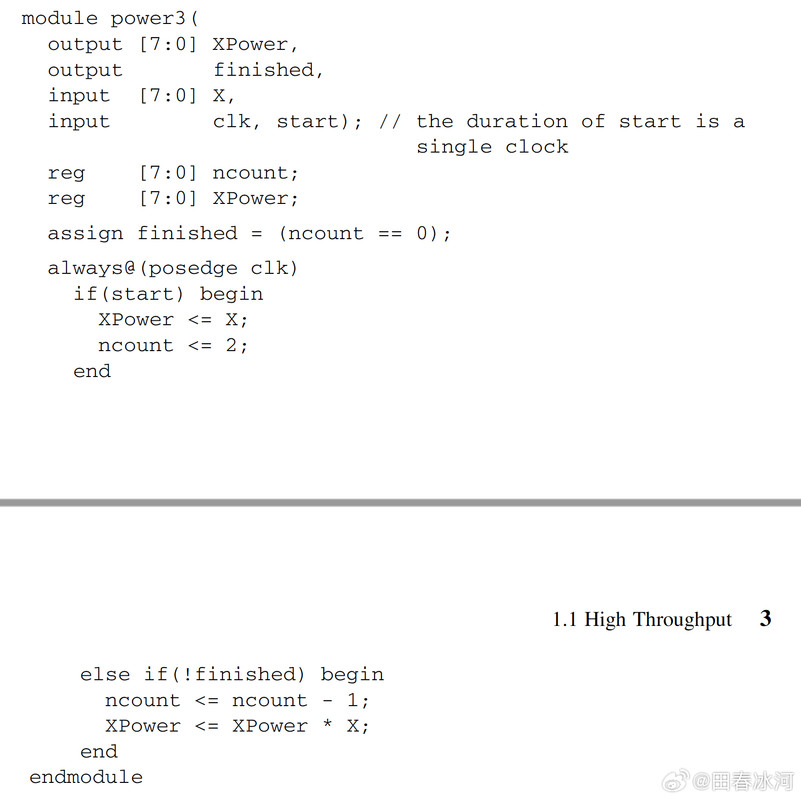

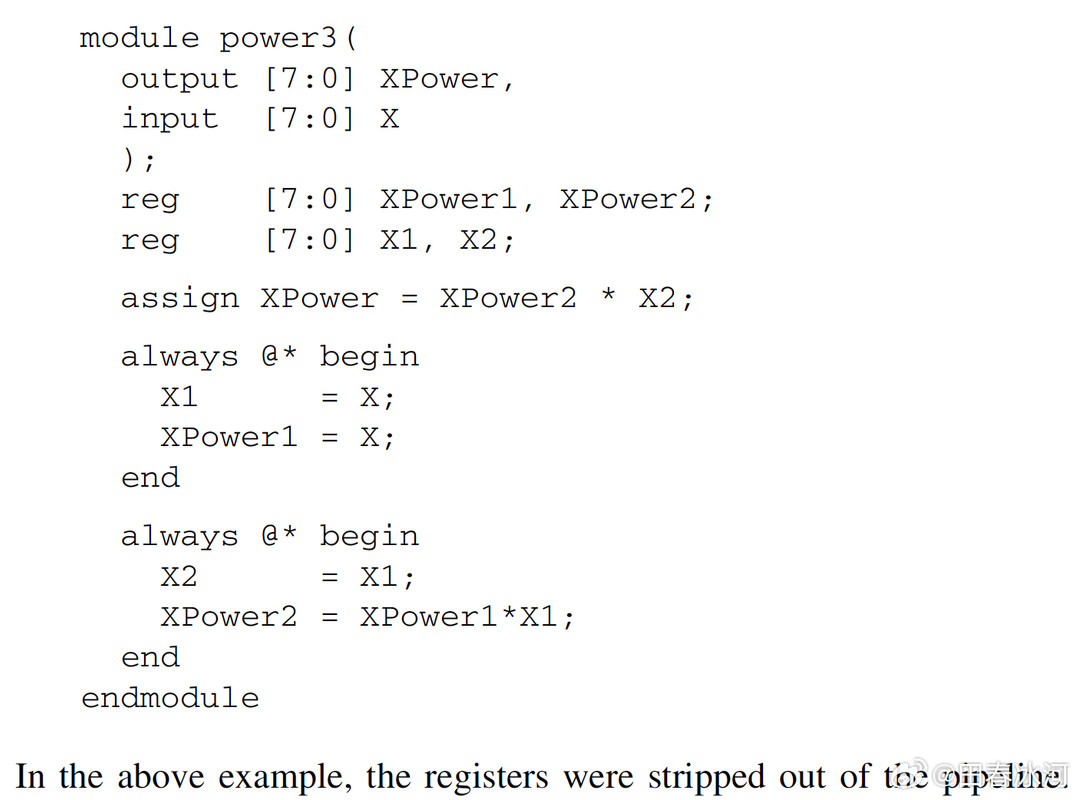

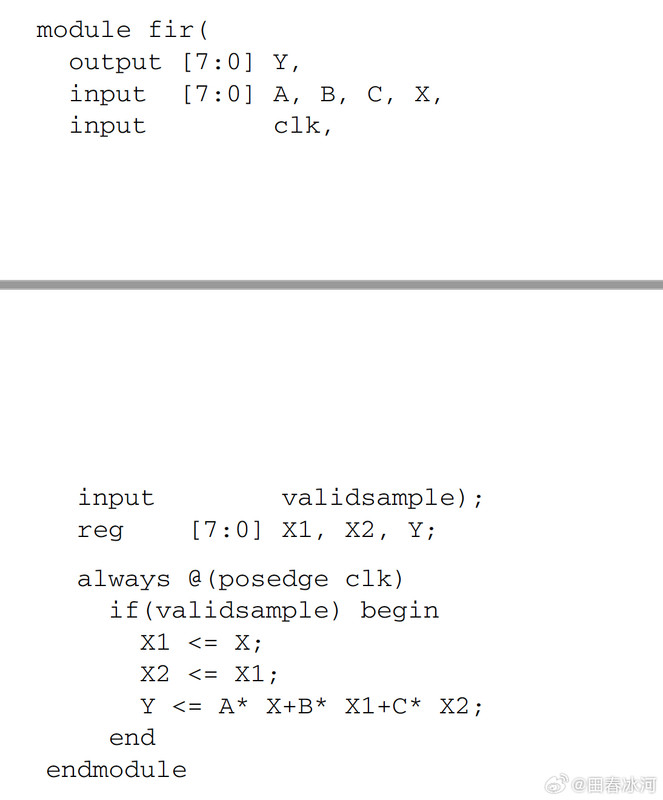

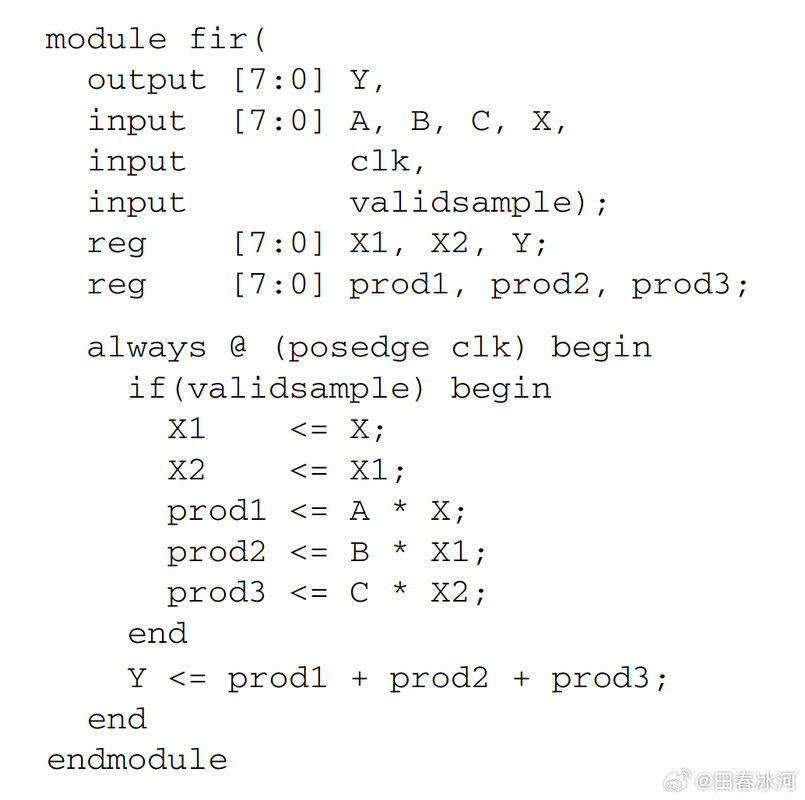

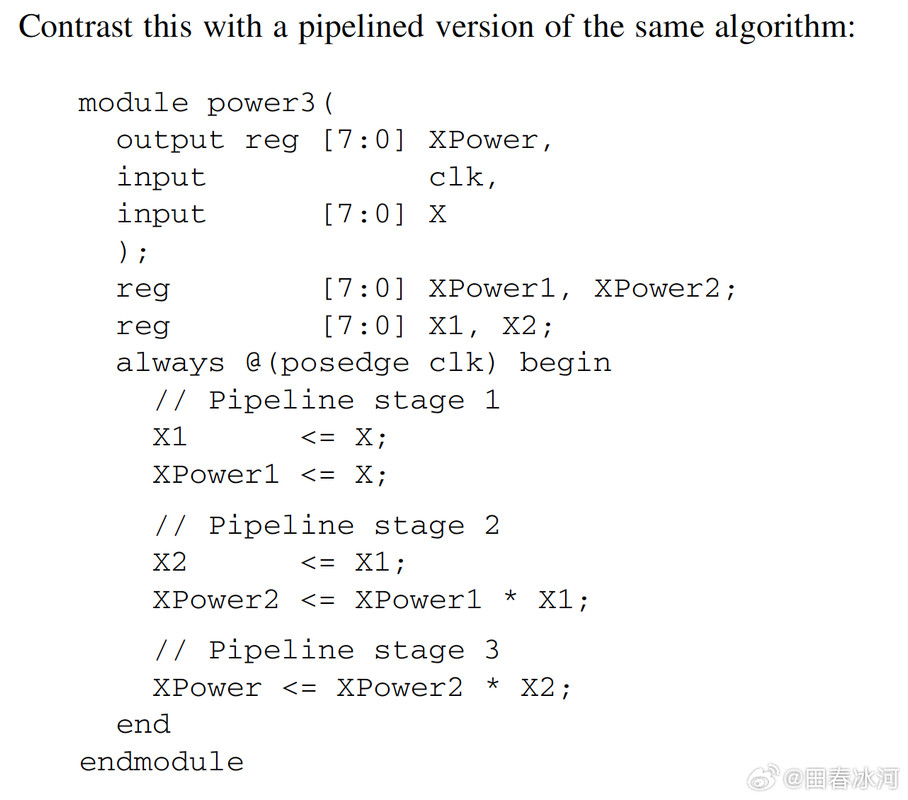

[1/3] 在数字电路里,把迭代循环展开成流水线可以大幅提高吞度量,但要牺牲芯片面积(FPGA 通常最缺的就是这个);去掉流水线中的寄存器可以大幅降低电路延迟,但要牺牲芯片的最大工作频率;要想提高工作频率可以增加中间寄存器将关键路径打断成较小的路径,但这又重新增加了延迟(不过幸好还有其他办法)。这些还都是小事,最缺德的是实现这些不同的设计思路对应的 VHDL/Verilog 代码从软件编程的视角看起来几乎没什么区别……

https://postimg.cc/gallery/fN34tD3

[1/3] 在数字电路里,把迭代循环展开成流水线可以大幅提高吞度量,但要牺牲芯片面积(FPGA 通常最缺的就是这个);去掉流水线中的寄存器可以大幅降低电路延迟,但要牺牲芯片的最大工作频率;要想提高工作频率可以增加中间寄存器将关键路径打断成较小的路径,但这又重新增加了延迟(不过幸好还有其他办法)。这些还都是小事,最缺德的是实现这些不同的设计思路对应的 VHDL/Verilog 代码从软件编程的视角看起来几乎没什么区别……

https://postimg.cc/gallery/fN34tD3